SW Tools

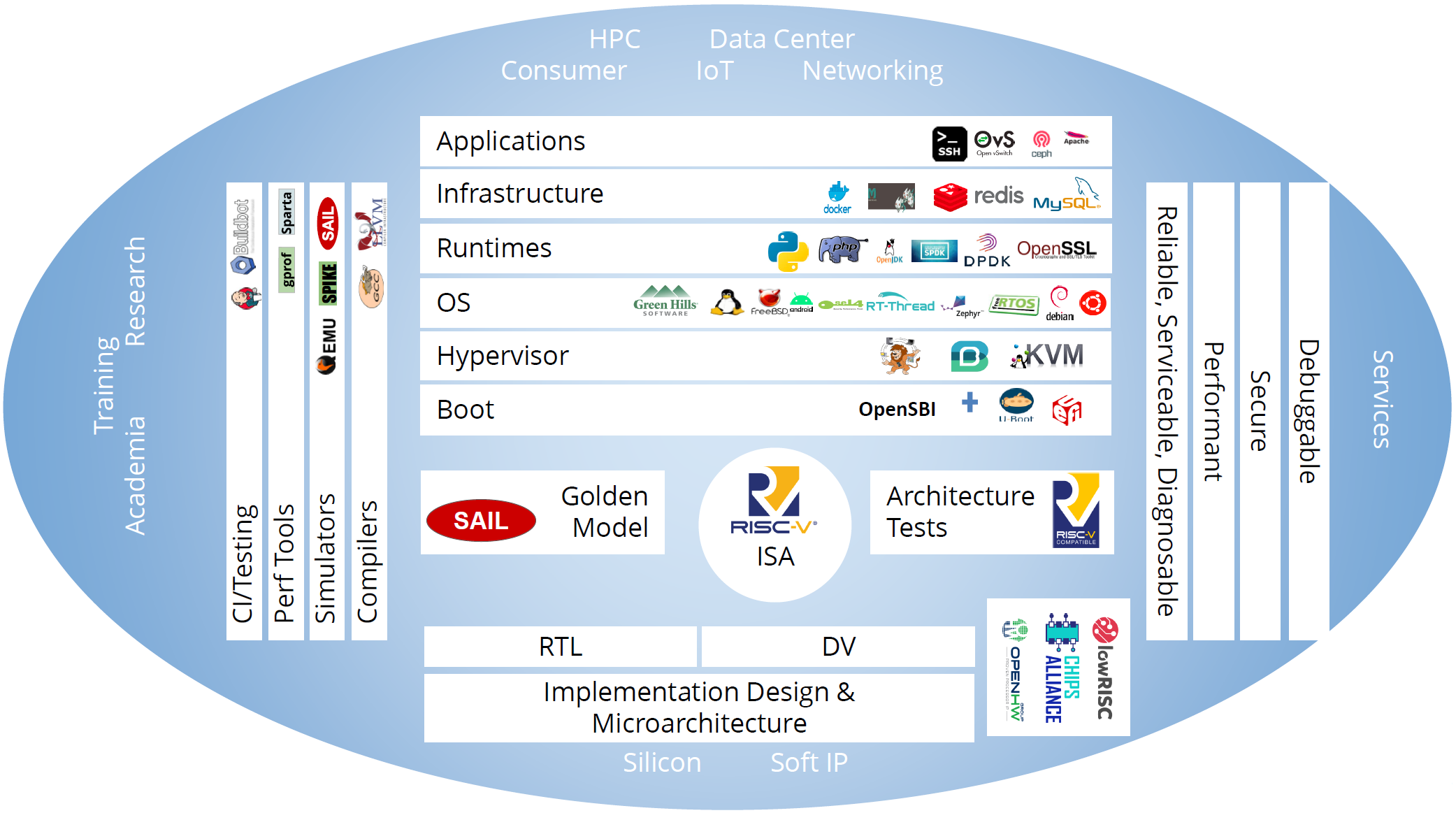

The RISC-V SW ecosystem is diverse and rapidly growing, with stable OS, emulators, compilers, binutils, number of RTOS/kernel ports and other SW packages available.

Syntacore Development Toolkit

Syntacore Development Toolkit for RISC-V (SC-DT) is designed to create applications for SCRx cores.

It contains the latest releases of pre-built and pre-configured tools optimized for Syntacore SCRx cores.

The toolkit include the following basic packages:

- LLVM/clang — supports advanced optimization out of the box, micro-architecture aware optimizations and -mtune=scr1..scr9, includes RVV autovectorization, CRC recognition and other features,

- RISCV GCC with Assembler, Linker, Binutils, and Standard C/C++ libraries for Linux and bare-metal environments (Newlib and Glibc),

- GNU GDB — supports single and multicore configurations and Python scripts,

- OpenOCD — fine-tuned version with set of scripts for supported probes setup,

- QEMU:

- System level with SCR1-SCR9 platforms,

- User level for Linux applications,

- BSP — example boards support package for different platforms: variety set of FPGA boards and simulators,

- IDE*:

- Eclipse IDE — mature IDE with all targets support (QEMU, OpenOCD, GDB, and remote debugging) and embedded examples,

- VSCode integration data**,

- Sample applications and benchmarks for FPGA-based SDKs, FreeRTOS, and bare-metal environments.

*Syntacore RISC-V development tools can also be used from the command-line interface.

**The VSCode IDE is not included in the toolkit and should be downloaded and installed separately.

We recommend to have a look at the Installation Guide before downloading and installing the toolkit.

This guide has important preliminaries for your host system.

Information on current release features and improvements can be found in Release Notes.

Toolkit is available for Windows and Linux OS. Download links and MD5 checksum info are presented below.

Windows sc-dt-2023.11-win.zip (1.15 Gb) 5cfedf4a23681bb6044d75c17d744bdc5f5deeea (MD5) |

Linux sc-dt-2023.11.tar.gz (900.6 Mb) 3baa0bf1f3d6623cd407de330b1a214abbbbbcea (MD5) |

RISCV64 sc-dt-Linux-riscv64-2023.11.tar.gz (886.1 Mb) d4e750526b8dd0e43caf17126f879ae119336df6 (MD5) |

Installation Guide

Syntacore_Development_Toolkit_Installation_Guide.pdf (715 Kb)

(MD5 checksum: 999d17f8bb73dc82e2ccc44124b6b9c8634a028b)

Release Notes

Syntacore_Development_Toolkit_Release_Notes.pdf (392 Kb)

(MD5 checksum: 727917804924d386bfce336e219602a93923538a)

User Guide

Syntacore_Development_Toolkit_Guide.pdf (4.4 Mb)

(MD5 checksum: 4777440305a146aa751240d97550086e1a898b08)

Open-source SW for RISC-V

Some details on other SW supporting RISC-V and not included into the SC-DT can be found below.

Simulators:

- Spike, the RISC-V ISA Simulator, implements a functional model of one or more RISC-V harts.

- gem5 is a modular platform for computer-system architecture research, encompassing system-level architecture as well as processor microarchitecture.

OS:

- Linux kernel is customized for SCRx cores and supported within community.

- Zephyr is customized for SCRx cores and supported within community.

- FreeBSD has an architecture port for RISC-V.

- Gentoo, a highly flexible, source-based Linux distribution. Gentoo:RISC-V is the architecture support project.

- sel4 — The benchmark for performance. A microkernel supporting RISC-V.

- Rtems — The Real-Time Executive for Multiprocessor Systems is an open source RTOS that supports open standard application programming interfaces (API).

- Mynewt — An OS to build, deploy and securely manage billions of devices.

Runtimes:

- OpenJDK/HotSpot has an JEP 422: Linux/RISC-V Port and Syntacore openjdk-17 (LTS) with jep422 backport.

Languages:

Libraries: