SCR1 Microcontroller Core

Minimalistic 32-bit MCU core for deeply embedded applications and accelerator control. It can be configured for a very small area - under 15kGates in a fully-fuctional configuration, and is open-sourced under the permissive SHL license, which allows commercial use.

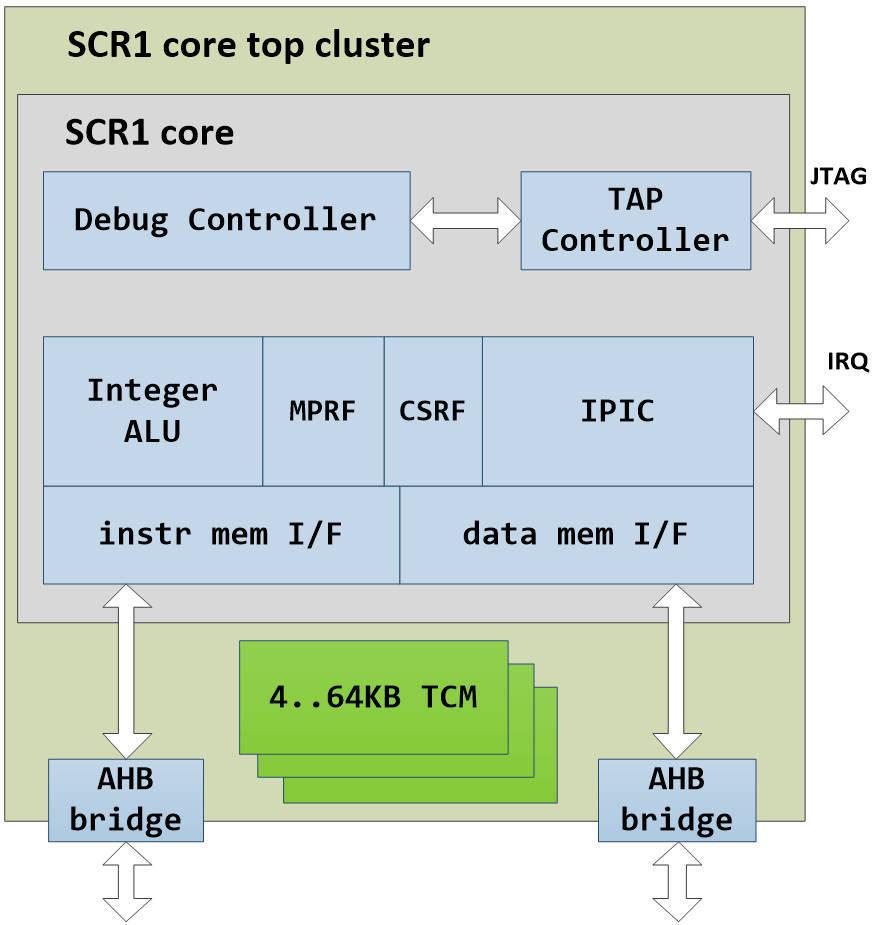

Block diagram

Key features

- 32bit microcontroller core with RISC-V ISA

- RV32I|E[MC]

- Harvard architecture, separate Instruction and Data memories

- 32 or 16 32bit integer registers

- RV32I or E basic instruction set, optional M and C extensions

- 47 Integer (32bit encoding) instructions

- 47 E instructions (subset of I, restricted to 16 registers)

- 27 Compact (16 bit encoding) instructions

- 8 Optional Multiply/Divide instructions

- 15 kGates in basic fully functional configuration (ICE)

- Includes IRQ controller and debug

- 32bit AHB-compliant external interface

- 2 to 4 stages pipeline

- Machine-mode only

- Embedded 64bit RTC timer

- Tightly Coupled Memory (TCM) support

- 4..64KB

- Optional configurable Integrated Programmable Interrupt Controller (IPIC)

- Low interrupt latency

- 8..32 IRQs

- Optional area-optimized MUL/DIV unit

- Optional integrated Debug Controller

- with JTAG-compliant interface

Full RTL and supplimentary collateral are avaialble from our github repository:

- Verification suite

- Testbench, tests, tracelog

- Documentation

- Basic simulation and synthesisenv

- Reference design

- Open FPGA-based SDKs