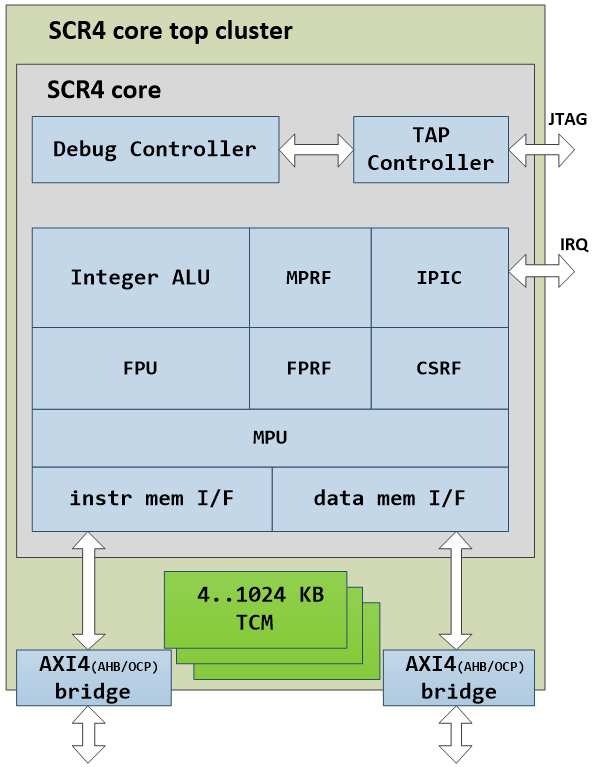

SCR4 Microcontroller Core (RV32 or RV64)

High-performance 32 or 64bit multicore capable MCU core with FPU

Block diagram

Key features

- Harvard architecture (separate instruction and data buses)

- RV32IMCF[DA] or RV64IMCF[DA] ISA

- User and Machine privilege modes

- High-performance IEEE 754-2008 compliant floating-point unit

- Configurable single or double precision FP unit

- Register file of 32 floating-point data registers

- Configurable high-performance or area-optimized multiply/divide unit

- Configurable 3 to 5 stage pipeline implementation

- Configurable AXI4 or AHB external memory interface

- Tightly Coupled Memory (TCM) support, L1 caches ECC/parity

- Optional MPU (Memory Protection Unit)

- Optional configurable Integrated Programmable Interrupt Controller (IPIC) and PLIC

- up to 1024 IRQs

- Low interrupt latency

- Advanced Integrated Debug Controller

- JTAG compliant interface

- HW/SW breakpoints support

- ROM breakpoints support

- Multicore configs up to 4 SCRx cores

- SMP and heterogeneous

- with memory coherency

Request further details.