Высокопроизводительное 64-битное ядро уровня приложений SCR7 c улучшенными характеристиками

Общие сведения

Программа для ЭВМ «Высокопроизводительное 64 битное ядро уровня приложений SCR7 c улучшенными характеристиками» (далее по тексту ПО SCR7) представляет собой реализацию процессора архитектуры RISC-V микропроцессорного класса для встроенных применений с поддержкой Linux-подобных операционных систем.

ПО SCR7 предназначено для работы в составе систем на кристалле (СнК), реализованных непосредственно в кремнии или в программируемых логических интегральных схемах (ПЛИС), и может применяться в одноядерных и многоядерных конфигурациях.

ПО SCR7 является сложным функциональным СФ-блоком (Soft IP), передаваемым потребителю в виде описания на высокоуровневом языке описания аппаратуры SystemVerilog для дальнейшего использования в программах автоматизированного синтеза логических схем с привязкой к конкретной технологии ASIC или ПЛИС.

ПО разрабатывается с использованием собственных мощностей и ресурсов. Цена является договорной, размер вознаграждения за право использования зависит от конфигурации ПО. Обновление ПО производится силами разработчика.

Функциональные характеристики

ПО SCR7 реализует собой 64-х разрядный процессор архитектуры RISC-V микропроцессорного класса, предназначенный для использования в составе различных встраиваемых и других систем, где требуется полнофункциональная поддержка ОС Linux.

Программа обеспечивает выполнение арифметических и логических операций с целочисленными операндами и вычислений с плавающей точкой одинарной и двойной точности; поддержку 16- и 32- битных инструкций и 64/32/16/8-битных операндов; идентификацию ядер в многоядерных конфигурациях СнК;

Основные функциональные характеристики ПО SCR7:

- Гарвардская архитектура (раздельные шины команд и данных);

- Поддержка симметричной многопроцессорности (SMP) и межъядерного взаимодействия с настраиваемой конфигурацией от 1 до 8 процессорных ядер в кластере;

- Набор команд: RV64IMСAFD

- базовый набор с целочисленными операциями, 64-битный (RV64I);

- команды операций целочисленное умножения и деления (М расширение);

- команды компактного формата для увеличения плотности кода (16-битовые, С расширение);

- атомарные операции (А расширение);

- арифметические операции с плавающей точкой над числами одинарной точности (Single-Precision Floating-Point, F расширение);

- арифметические операции с плавающей точкой над числами двойной точности (Double-Precision Floating-Point, D расширение);

- Три уровня привилегированности и соответствующих им режимов исполнения команд: машинный уровень (режим M-mode), пользовательский уровень (режим U-mode), уровень супервизора (режим - S-mode);

- Многоуровневый конвейер с реализацией внеочередного исполнения команд;

- Высокопроизоводительный модуль операций с плавающей запятой одинарной и двойной точности (Floating-Point Unit);

- Конфигурируемая подсистема памяти:

- поддержка виртуальной памяти с помощью модуля управления памятью (MMU);

- контроль доступа к физической памяти с помощью модуля защиты памяти (MPU - Memory Protection Unit);

- опциональная поддержка памяти быстрого доступа (ТСМ, Tightly-Coupled Memory) до 512 Кб;

- поддержка кэш-памяти L1 и L2 (с опцией коррекции ошибок) с когерентностью памяти:

- кэш команд уровня L1 размером от 8 до 64 Кб;

- кэш данных уровня L1 размером от 8 до 64 Кб;

- поддержка кэш данных уровня L2 размером до 2 Мб на кластер;

- Поддержка конфигурируемого контроллера прерываний уровня платформы (PLIC) с возможностью приема большого количества внешних запросов прерываний (до 1023) и с динамическим заданием (изменением) приоритета прерываний;

- Встроенный 64-битовый таймер часов реального времени (Real Time Clock) с настраиваемым коэффициентом деления;

- Встроенный контроллер отладки с поддержкой аппаратных точек останова, совместимый со стандартом IEЕЕ 1149.1-2001 (JTAG);

- Конфигурируемый внешний интерфейс, совместимый с шиной AXI (Advanced extensible Interface) с поддержкой когерентности в многоядерной системе - расширение ACE (AXI Coherency Extensions).

Состав ПО

ПО SCR7 в базовой конфигурации, реализующей архитектуру RV64IMСAFD включает в себя:

- Исходный код на языке SystemVerilog, пригодный для моделирования и синтеза;

- Исходный код тестового окружения (Testbench) для выполнения функциональной верификации до и после синтеза;

- Наборы скриптов для проведения моделирования и синтеза с файлами входных ограничений в формате (.sdc).

- Комплект разработчика на базе ПЛИС (SCR7 SDK):

- пример проекта СнК на основе ПО SCR7;

- образы загрузки ПЛИС и объектных модулей прикладного ПО для выполнения на ядре SCR7.

- Инструментальные средства разработки:

- набор инструментальных средств, основанных на GCC 8.x, 9.x: компилятор, отладчик, компоновщик, функциональный симулятор, бинарные утилиты binutils, newlib, openocd;

- IDE на базе Eclipse (для Linux и Windows).

- Прикладное ПО:

- начальный загрузчик;

- набор архитектурных тестов и тестов совместимости;

- примеры простых приложений (baremetal) и тестов производительности;

- операционная система Linux для платы SCR7 SDK.

- Сопроводительная документация:

- руководство пользователя ПО SCR7 (SCR7 UM);

- спецификация внешней архитектуры ПО SCR7 (SCR7 EAS);

- руководство по системе команд (SCR7 ISM);

- руководство на комплект разработчика (SCR7 SDK);

- руководство по инструментам разработчика (SCRx development tools);

- руководство на тестовое окружение.

Требования к работе с ПО

Типом реализующей ЭВМ для ПО SCR7 является Система-на-Кристалле (СнК) в составе полузаказных интегральных микросхем или программируемых логических интегральных схем (ПЛИС).

При реализации собственных функционально законченных СнК пользователь должен самостоятельно дополнить основу (микропроцессорную структуру ПО SCR7) необходимыми ему дополнительными модулями в виде отдельных IP-ядер или инфраструктурами IP-ядер.

Для логического синтеза и функциональной верификации ПО SCR7 в составе СнК, пользователю предоставляется набор средств разработки “SCR7 SDK” для физического прототипирования на ПЛИС, основными компонентами которого являются:

- пример проекта СнК для ПЛИС на основе ПО SCR7;

- Предварительно собранные образы процессорного ядра ПО SCR7, начального загрузчика и ОС Linux;

- Тестовое программное обеспечение для проверки работоспособности ПО SCR7.

Необходимое обеспечение для работы с ПО SCR7

Для работы с ПО SCR7 необходимо следующее обеспечение:

- Персональный компьютер (ПК) с объёмом оперативной памяти не менее 8 Гб.

- Установленные на ПК программы:

- ОС Windows или Linux;

- пакет программ Xilinx Vivado WebPack Edition версии не ниже 2018.1 (скачивается бесплатно после регистрации на сайте xilinx.com);

- система отладки OpenOCD.

- Отладочная плата Virtex UltraScale+ FPGA VCU118 Evaluation Kit

(https://www.xilinx.com/products/boards-and-kits/vcu118.html). - Адаптер для соединения с отладчиком OpenOCD (JTAG Cable Adapter): Olimex ARM-USB-OCD-H (or ARM-USB-OCD)

(https://www.olimex.com/Products/ARM/JTAG/ARM-USB-OCD-H/). - Переходная плата

(https://www.xilinx.com/products/boards-and-kits/hw-fmc-xm105-g.html). - Набор стандартных кабелей типа USB Type A (m) - Type B micro (m), 3 шт. (из состава комплектов платы VCU118 и JTAG адаптера).

- Кабель Ethernet cat.5E (в комплекте VCU118 Evaluation Kit).

Компиляция ПО

Процесс компиляции образа ПО SCR7 описан в руководстве на комплект разработчика (SCR7 SDK). В состав ПО входит Zip-архив, содержащий скомпилированные образы, созданные согласно руководству на комплект разработчика пример проекта СнК на основе ПО SCR7. В следующих разделах описан процесс установки и тестирования ПО SCR7 в составе проекта СнК.

Установка ПО

Процесс установки ПО заключается в выполнении процедуры программирования конфигурационного ППЗУ (флэш) на отладочной плате, для обеспечения дальнейшей загрузки ПЛИС.

Для установки и работы с ПО SCR7 персональный компьютер подключается к отладочной плате VCU118 стандартными кабелями типа USB Type A (m) - Type B micro (m).

Подключение кабелей к отладочной плате VCU118

- Подключите один кабель "USB Type A (m) - Type B micro (m)" между хост компьютером и портом USB JTAG (J106) на плате VCU118;

- Подключите второй кабель "USB Type A (m) - Type B micro (m)" между хост компьютером и портом USB UART на плате VCU118;

- Подключите кабель источника питания (есть в комплекте платы) к разъему "Power" платы VCU118.

Это подключение выполняет три функции:

- Подачу питания +12В на отладочную VCU118;

- Обеспечение конфигурирования ПЛИС через USB JTAG порт;

- Обеспечение функциональности консольного порта при выполнении программы на процессорном ядре SCR7 через USB UART порт.

Подключение кабелей к отладочной плате VCU118 приведено на Рисунке 1.

Рисунок 1: Подключение кабелей к отладочной плате VCU118

- Распакуйте архив, находящийся в дереве каталогов ПО SCR7 в папке SDK:<

SDK_HOME >/images/vcu118_scr7.tar.gz. В архиве находятся два файла: vcu118_scr7.mcs, vcu118_scr7.prm. - После подачи питания на плату VCU118, запустите пакет программ Vivado на инструментальном ПК.

- Проверьте подключение кабеля USB JTAG, затем запустите утилиту «Hardware Manager» из меню или командной строки консоли Vivado. Выполните команду «Open Target» с опцией «Auto Connect», должно произойти подключение к микросхеме ПЛИС xcvu9p_0 отладочной платы VCU118 по интерфейсу JTAG.

Примечание: Если подключение не произошло (микросхемы нет в списке обнаруженных), необходимо установить необходимые USB-драйвера для ОС Windows или для ОС Linux настроить правила сервиса UDEV-rules, как описано в AR# 66440 Vivado - Linux OS - Digilent and Xilinx USB cable installation check

- Добавьте в конфигурационную цепочку для программирования микросхему конфигурационной flash. Для этого в меню «Hardware» выделите указателем «мыши» микросхему ПЛИС xcvu9p_0 и по нажатию правой кнопки «мыши» в контекстном меню указателем выберете «Add Configuration Memory Device».

- В открывшемся меню выберите (или введите) тип микросхемы flash: mt25qu01g-spi-x1_x2_x4 и нажмите OK

- На вопрос программатора ”Do you want to program the configuration memory device now?", подтвердите “OK”.

- В открывшимся диалогом окне «Program Configuration Memory Device» добавьте загрузочные файлы образов «прошивки» ПЛИС (см. выше: vcu118_scr7.mcs, vcu118_scr7.prm)

- Нажмите “OK” для запуска процесса программирования конфигурационной микросхемы flash (процесс программирования может занять несколько минут).

Примечание: Проверьте, что DIP переключатель SW16 на плате VCU118 установлен в положение выбора режима загрузки ПЛИС Master SPI

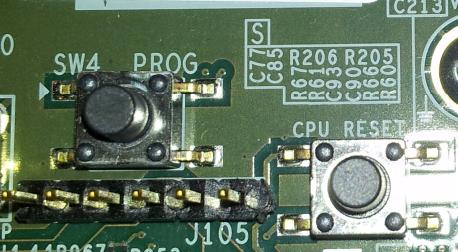

- После успешного завершения процесса программирования (можно проконтролировать по сообщениям в диалоговом окне), необходимо выйти из программы Vivado и загрузить образ «прошивки» в ПЛИС, для этого нажмите кнопку “PROG” на отладочной плате VCU118, или нажмите кнопку “CPU_RESET” на плате (см. рисунок ниже), или выключите и включите плату.

Рисунок 2: Аппаратный сброс платы VCU118

ПО SCR7 установлено и готово к работе.

Загрузка и запуск образа ОС Linux на платформе SCR7 SDK с использованием OpenOCD

В качестве теста работоспособности ПО SCR7 в составе проекта СнК используется запуск ОС Linux на платформе SCR7 SDK.

Open On-Chip Debugger (открытый отладчик для чипов) является программой с открытым исходным кодом. OpenOCD предоставляет доступ к адаптеру для отладки (JTAG debug adapter) и обеспечивает инструментарий отладки (debugging) и внутрисхемного программирования для встраиваемых систем.

Подключение JTAG кабеля адаптера OpenOCD

Подключение JTAG кабеля адаптера Olimex ARM-USB-OCD к плате VCU118 (см. рисунок ниже) выполняется с помощью переходной платы FMC XM105, имеющей в своем составе пользовательский разъемом J20 для подключения стандартного 20-ти контактного гибкого шлейфа.

Примечание: Перед первым подключением платы XM105, необходимо настроить необходимый уровень напряжения питания на разъеме FMC платы VCU118 с помощью утилиты VCU118 System Controller GUI tool, работающей под управлением ОС Windows (Win10)

Полное руководство для утилиты доступно по ссылке: VCU118 System Controller Tutorial.

Утилита и руководство к ней скачиваются бесплатно после авторизации на сайте https://www.xilinx.com

Необходимо соединить выводы TDI и TDO на разъеме J5 платы FMC XM105 (JTAG chain bypass).

Рисунок 3: Подключение JTAG кабеля адаптера OpenOCD к плате VCU118

Установка OpenOCD

Инструкции по установке OpenOCD приведены на вики-странице OpenOCD-for-sc_riscv32

Запуск сервера OpenOCD на ПК

- Настройка переменных окружения:

$ export OOCD_ROOT=<Раth to the OpenOCD installation directory>

- Запуск OpenOCD сервера - вводится в одну строку (в Ubuntu):

$ ${OOCD_ROOT}/bin/openocd -s ./share/openocd/scripts \ -f ${OOCD_ROOT}/share/openocd/scripts/interface/ftdi/olimex-arm-usb-ocd-h.cfg \ -f ${OOCD_ROOT}/share/openocd/scripts/target/syntacore_riscv_quad.cfgПосле выполнения в текущий терминал будет выдано сообщение о подключении к ядрам RISC-V:

$ ./bin/openocd -s ./share/openocd/scripts -f ./share/openocd/scripts/interface/ftdi/olimex-arm-usb-ocd-h.cfg -f ./share/openocd/scripts/target/syntacore_riscv_quad.cfg Open On-Chip Debugger 0.10.0+dev-01974-g3d33e05 (2019-05-22-20:30) Licensed under GNU GPL v2 For bug reports, read http://openocd.org/doc/doxygen/bugs.html sw_reset_halt Info : Listening on port 6666 for tcl connections Info : Listening on port 4444 for telnet connections adapter speed: 2000 kHz trst_and_srst separate srst_gates_jtag trst_push_pull srst_open_drain connect_deassert_srst Info : auto-selecting first available session transport "jtag". To override use 'transport select <

transport >'. Info : clock speed 2000 kHz Info : JTAG tap: scr7_core0.cpu tap/device found: 0xdab17001 (mfg: 0x000 (< invalid >), part: 0xab17, ver: 0xd) Info : JTAG tap: scr7_core1.cpu tap/device found: 0xdbb17001 (mfg: 0x000 (< invalid >), part: 0xbb17, ver: 0xd) Info : JTAG tap: scr7_core2.cpu tap/device found: 0xdcb17001 (mfg: 0x000 (< invalid >), part: 0xcb17, ver: 0xd) Info : JTAG tap: scr7_core3.cpu tap/device found: 0xddb17001 (mfg: 0x000 (< invalid >), part: 0xdb17, ver: 0xd) Info : scr7_core0.cpu: datacount=4 progbufsize=6 Info : scr7_core0.cpu: Exposing additional CSR 3008 Info : scr7_core0.cpu: Exposing additional CSR 3009 Info : scr7_core0.cpu: Exposing additional CSR 3010 Info : scr7_core0.cpu: Exposing additional CSR 3011 Info : scr7_core0.cpu: Exposing additional CSR 3012 Info : scr7_core0.cpu: Exposing additional CSR 3013 Info : scr7_core0.cpu: Exposing additional CSR 3014 Info : scr7_core0.cpu: Exposing additional CSR 3015 Info : scr7_core0.cpu: Exposing additional CSR 4033 Info : scr7_core0.cpu: Exposing additional CSR 4034 Info : scr7_core0.cpu: Examined RISC-V core; found 1 harts Info : scr7_core0.cpu: hart 0: XLEN=64, misa=0x800000000014112d Info : scr7_core1.cpu: datacount=4 progbufsize=6 Info : scr7_core1.cpu: Exposing additional CSR 3008 Info : scr7_core1.cpu: Exposing additional CSR 3009 Info : scr7_core1.cpu: Exposing additional CSR 3010 Info : scr7_core1.cpu: Exposing additional CSR 3011 Info : scr7_core1.cpu: Exposing additional CSR 3012 Info : scr7_core1.cpu: Exposing additional CSR 3013 Info : scr7_core1.cpu: Exposing additional CSR 3014 Info : scr7_core1.cpu: Exposing additional CSR 3015 Info : scr7_core1.cpu: Exposing additional CSR 4033 Info : scr7_core1.cpu: Exposing additional CSR 4034 Info : scr7_core1.cpu: Examined RISC-V core; found 1 harts Info : scr7_core1.cpu: hart 0: XLEN=64, misa=0x800000000014112d Info : scr7_core2.cpu: datacount=4 progbufsize=6 Info : scr7_core2.cpu: Exposing additional CSR 3008 Info : scr7_core2.cpu: Exposing additional CSR 3009 Info : scr7_core2.cpu: Exposing additional CSR 3010 Info : scr7_core2.cpu: Exposing additional CSR 3011 Info : scr7_core2.cpu: Exposing additional CSR 3012 Info : scr7_core2.cpu: Exposing additional CSR 3013 Info : scr7_core2.cpu: Exposing additional CSR 3014 Info : scr7_core2.cpu: Exposing additional CSR 3015 Info : scr7_core2.cpu: Exposing additional CSR 4033 Info : scr7_core2.cpu: Exposing additional CSR 4034 Info : scr7_core2.cpu: Examined RISC-V core; found 1 harts Info : scr7_core2.cpu: hart 0: XLEN=64, misa=0x800000000014112d Info : scr7_core3.cpu: datacount=4 progbufsize=6 Info : scr7_core3.cpu: Exposing additional CSR 3008 Info : scr7_core3.cpu: Exposing additional CSR 3009 Info : scr7_core3.cpu: Exposing additional CSR 3010 Info : scr7_core3.cpu: Exposing additional CSR 3011 Info : scr7_core3.cpu: Exposing additional CSR 3012 Info : scr7_core3.cpu: Exposing additional CSR 3013 Info : scr7_core3.cpu: Exposing additional CSR 3014 Info : scr7_core3.cpu: Exposing additional CSR 3015 Info : scr7_core3.cpu: Exposing additional CSR 4033 Info : scr7_core3.cpu: Exposing additional CSR 4034 Info : scr7_core3.cpu: Examined RISC-V core; found 1 harts Info : scr7_core3.cpu: hart 0: XLEN=64, misa=0x800000000014112d Info : Listening on port 3333 for gdb connections Info : Listening on port 3334 for gdb connections Info : Listening on port 3335 for gdb connections Info : Listening on port 3336 for gdb connections - Откройте второй терминал (терминал 2) и введите команду:

$ telnet localhost 4444 Trying ::1... Trying 127.0.0.1... Connected to localhost. Escape character is '^]'. Open On-Chip Debugger

В терминале 1 выводится подтверждение запуска telnet сессии:

Info : accepting 'telnet' connection on tcp/4444

OpenOCD запущен и готов к работе. Терминал 2 представляет собой интерактивную консоль OpenOCD.

По команде help можно вывести список доступных команд openocd.

Загрузка и запуск на выполнение бинарного образа ОС Linux на платформе SCR7 SDK

Примечание: При загрузке с OpenOCD используются образы двоичных файлов в формате .elf или .bin

- Введите следующие команды в консоли OpenOCD (Терминал 2), выполняющие остановку ядра и загрузку исполняемого кода:

> targets TargetName Type Endian TapName State -- ------------------ ---------- ------ ------------------ ------------ 0 scr7_core0.cpu riscv little scr7_core0.cpu running 1 scr7_core1.cpu riscv little scr7_core1.cpu running 2 scr7_core2.cpu riscv little scr7_core2.cpu running 3* scr7_core3.cpu riscv little scr7_core3.cpu running > targets scr7_core0.cpu > targets TargetName Type Endian TapName State -- ------------------ ---------- ------ ------------------ ------------ 0* scr7_core0.cpu riscv little scr7_core0.cpu running 1 scr7_core1.cpu riscv little scr7_core1.cpu running 2 scr7_core2.cpu riscv little scr7_core2.cpu running 3 scr7_core3.cpu riscv little scr7_core3.cpu running > halt ; load_image vmlinux.bin; resume 0xffffffffffffff04 8895708 bytes written at address 0x00000000 downloaded 8895708 bytes in 85.746063s (101.313 KiB/s)

Примечание: Команда загрузки предполагает расположение файла в текущей директории. При другом расположении, имя загружаемого файла должно включать относительный путь.

- После ввода команды отображается прогресс загрузки. После завершения загрузки начнется стандартная загрузка Linux с выводом лога в терминал uart:

vvvvvvvvv SSSSSSS rrrr vvvvvvv SS s TM rrrrrr vvvvvv SS s s sss ssss sss sss sss sss sss rrrrrr vvvvv SSSSSS s s s s s s s s s s s s rrrr vvvvv SS s s s s s sssss s s s s sssss rr vvvvvv r SS ssss s s s s s s s s s s rrr vvvvv rr SSSSSSS s s s ss sss sss sss s sss rrrr vvv rrr sss rrrrr v rrrr rrrrrr rrrrr CUSTOM CORES AND TOOLS [ 0.000000] Linux version 4.19.166-46819-g5ceb3097ff34-dirty (mike@lynx2) (gcc version 10.2.0 (GCC)) #1 SMP Thu Jun 10 17:53:24 MSK 2021 [ 0.000000] bootconsole [early0] enabled [ 0.000000] initrd not found or empty - disabling initrd [ 0.000000] SCRxDMA: created DMA memory pool at 0x00000000ff000000, size 16 MiB [ 0.000000] OF: reserved mem: initialized node scr-dma@fe000000, compatible id scr-sdk-dma-pool [ 0.000000] Zone ranges: [ 0.000000] DMA32 [mem 0x0000000000000000-0x00000000feffffff] [ 0.000000] Normal empty [ 0.000000] Movable zone start for each node [ 0.000000] Early memory node ranges [ 0.000000] node 0: [mem 0x0000000000000000-0x00000000feffffff] [ 0.000000] Initmem setup node 0 [mem 0x0000000000000000-0x00000000feffffff] [ 0.000000] On node 0 totalpages: 1044480 [ 0.000000] DMA32 zone: 14280 pages used for memmap [ 0.000000] DMA32 zone: 0 pages reserved [ 0.000000] DMA32 zone: 1044480 pages, LIFO batch:63 ... ... ... [ 2.900000] vcu118_dp83867_phy_fixup: [ 2.900000] DP83867 phy: Switch to SGMII 6-wire mode [ 2.900000] IPv6: ADDRCONF(NETDEV_UP): eth0: link is not ready [ 3.920000] xilinx_axienet ffffffffff040000.ethernet eth0: Link is Down [ 6.000000] xilinx_axienet ffffffffff040000.ethernet eth0: Link is Up - 1Gbps/Full - flow control off [ 6.010000] IPv6: ADDRCONF(NETDEV_CHANGE): eth0: link becomes ready tcpsvd: listening on 0.0.0.0:21, starting Setup date/time... ---------------------------------------------------- System information Platform: vcu118_scr7 Firmware: SCR loader v1.3-g0b18395-dirty (Oct 18 2020 00:15:32) CPU clock, MHz: 90.000 ---------------------------------------------------- BusyBox v1.31.1 (2021-06-10 17:52:42 MSK) built-in shell (ash) Enter 'help' for a list of built-in commands. sdk@scr-sdk /$

- После выдачи приглашения “busybox”, Linux загружен и готов для использования.

- Выполнив следующие команды можно вывести информацию о загруженной операционной системе и процессорной платформе:

sdk@scr-sdk /$ uname -a Linux scr-sdk 4.19.166-46819-g5ceb3097ff34-dirty #1 SMP Thu Jun 10 17:53:24 MSK 2021 riscv64 GNU/Linux sdk@scr-sdk /$ cat /proc/cpuinfo processor : 0 hart : 0 isa : rv64imafdc mmu : sv39 uarch : syntacore,scr7 processor : 1 hart : 1 isa : rv64imafdc mmu : sv39 uarch : syntacore,scr7 processor : 2 hart : 2 isa : rv64imafdc mmu : sv39 uarch : syntacore,scr7 processor : 3 hart : 3 isa : rv64imafdc mmu : sv39 uarch : syntacore,scr7

Примеры программ для SCR7 SDK

Предоставляемый образ ОС Linux имеет встроенные бинарные файлы тестов, которые могут запускаться скриптом "benchmarks":

sdk@scr-sdk /$ benchmarks